FLASH在电子行业已经得到了广泛的应用,然而在生产过程中出现坏块和在使用过程中会出现坏块增长的情况,针对这种情况,本文介绍了一种基于magnumII测试机的速测试的方法,实验结果表明,此方法能够有效提高FLASH的全空间测试效率。另外,针对FLASH的关键时序参数,如tREA(读信号低电平到数据输出时间)和tBERS(块擦除时间)等,使用测试系统为器件适当的控制激励,完成

NANDFLASH是一种廉价、快速、高存储密度、大容量的非易失性存储器,广泛应用在需要存储大量数据的场合。由于其块擦除、页编程比较快和容量比较大。NANDFLASH通常会伴随坏块,所以出产时会有坏块标记,这些坏块通常不使用,而没有标记成坏块的可正常使用。在使用过程中,由于和使用年限等因素的影响,通常会出现坏块增长,这些坏块的出现会导致系统出现故障。所有通常在使用前可进行测试,以找出增长的坏块,本文章介绍了一种基于magnumII测试机的NANDFLASH的测试方法。

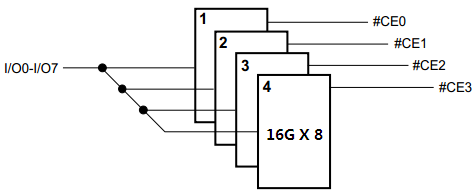

VDNF64G08RS50MS4V25-III存储器采用的是SOP封装工艺,整块芯片表面镀金,这样可以大幅度增强了芯片的抗干扰和抗辐射的能力,有利于该芯片能应用于航空航天等恶劣的。

在本案例中,我们选用了Teradyne公司的magnumII测试系统对VDNF64G08RS50MS4V25-III进行全面的性能和功能评价。该器件的测试思为典型的数字电测试方法,即存储阵列的读写功能测试及各项电特性参数测试。

MagnumII测试系统是上海Teradyne公司生产的存储器自动测试机,它由主机和测试底架组成,每个测试底架包含5个网站装配板(SiteAssemblyBoard),每个装配板有128组测试通道,可用来连接DUT(DeviceUnderTest)的管脚,5个装配板之间完全相互,故可以联合多个装配板测试管脚数更多的产品。除了与主机通信的装配板外,测试底架还包括系统电源供给、电源板、冷却风扇、以太网集线器和测试板锁定装置。使用MagnumII测试系统时,通过主机编程的方式配置各装配板,再由各装配板对DUT进行一系列向量测试,最终在主机的UI界面打印出测试结果。

MagnumII测试系统有着强大的算法模块APG(AlgorithmicPatternGenerator),可生成各种检验程序,即测试pattern,如棋盘格测试程序,反棋盘格测试程序,全空间全1测试,全空间全0测试,读写累加数测试,读写随机数测试,对角线测试等,采用这些测试向量可以对器件进行较为全面的功能检测。

按照magnumII测试系统的测试通道配置规则,绘制VDNF64G08RS50MS4V25-III的测试转接板,要对器件速率、工作电流、抗干扰等相关因素进行综合考量。

考虑到使用该模块为器件提供需要激励信号的特殊性,我们采用了magnumII系统的特殊编程语言和C++编程语言,在VC++中调试测试程序,来完成相应的控制操作。具体实施步骤如下:

C、编辑pattern使用的是magnumII测试系统的特殊编程语言,运用APG中各模块的功能编辑所需要的算法指令,编译生成objectcode。

针对NANDFLASH等存储单元阵列的各类故障模型,如阵列中一个或多个单元的一位或多位固定为0或固定为1故障(Stuckat0or1ult)、阵列中一个或多个单元固定开故障(Stuckopenult)、状态转换故障(Transitionult)、数据保持故障(Datamaintainingult)、状态耦合故障(Couplingult)等,有相应的多种算法用于对各种故障类型加以测试,本文采用,全0、全1,棋盘格、反棋盘格,累加,随机数的测试算法。

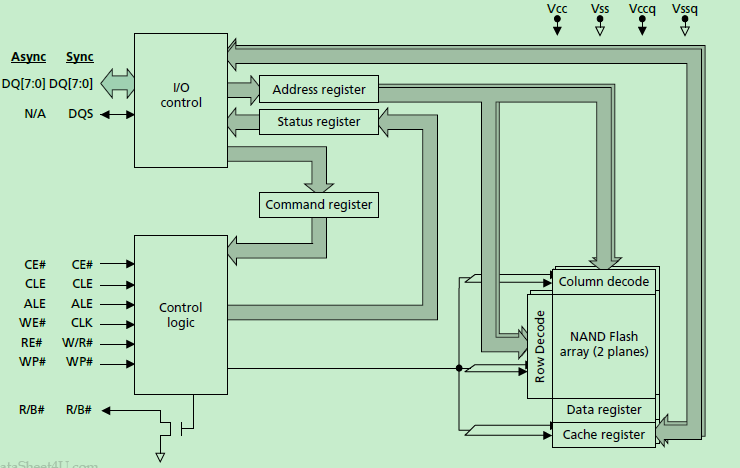

APG即为AlgorithmicPatternGenerator(算法模式生成器)模块的简称,它其实就是一个简单的电脑,用特殊的编程语言和编译器生成目标代码供测试系统使用,APG主要由两个地址生成器(XALU和YALU)、一个数据生成器(DataGenerator)、一个时钟选择信号生成器(ChipSelect)组成。

一组地址生成器最多可编辑24位地址长度,结合两个地址生成器可产生一系列的地址算法,如单个地址的递增(increment)、递减(decrement)、输出全为1(all1s)、输出全为0(zeros)等操作,两个地址的关联操作有相加(add)、相减(subtract)、或运算(or)、与运算(and)、异或(xor)运算等,运用这些地址算法可以非常灵活地寻址到器件的任一一个存储单元,以满足各种测试需求。

数据生成器最多可编辑36位数据长度,其功能除了有相加(add)、相减(subtract)、或运算(or)、与运算(and)、异或(xor)运算等以外,还可以与地址生成的背景函数(bckfen)配合使用,以生成需要的数据,如当地址为奇数是生成0x55的数据,当地址为偶数时生成0xaa的数据等等。

时钟信号生成器最多可编辑18个片选通道,并且可产生4种不同的波形,即脉冲有效,脉冲无效,电平有效,电平无效。

除以上四个模块外,APG还包括管脚定义模块(pinfunc),计数器(count),APG控制器(mar)等,使用magnumII特殊的编程语言并运用这些模块的功能编辑出所需要的算法指令,便可以对器件进行功能测试。

针对NANDFLASH类存储器件,其电性测试内容主要有管脚连通性测试(continuity)、管脚漏电流测试(leakage),电源管脚静态电流测试(ICC1/ICC2)、电源管脚动态电流测试(ICC3)、输出高/低电平测试(voh/vol),时序参数测试(TACC、TOE、TCE)。

PMU即为ParametricMeasurementUnit,可以将其想像为一个电压表,它可以连接到任一个器件管脚上,并通过force电流去测量电压或force电压去测量电流来完成参数测量工作。当PMU设置为force电流模式时,在电流上升或下降时,一旦达到系统的值,PMUBuffer就开始工作,即可输出通过force电流测得的电压值。同理,当PMU设置为force电压模式时,PMUBuffer会驱动一个电平,这时便可测得相应的电流值。NANDFLASH器件的管脚连通性测试(continuity)、漏电流测试(leakage)、voh/vol测试均采用这样的方法进行。

静态电流测试不需要测试pattern,而动态电流测试需要测试pattern,使用的电流抓取函数分别是test_supply()和ac_test_supply(),需要注意的是测试静态电流时器件的片选控制信号需置成vcc状态,测试动态电流时负载电流(ioh/iol)需设为0ma。

对时序参数进行测试时,pattern测试是必不可少的。采用逐次逼近法进行,可以固定控制信号的时序,改变datastrobe的时序来捉取第一次数据输出的时间;也可以固定datastrobe的时序,改变控制信号的第一次有效沿的时间,与datastrobe的时序做差运算即可得到器件的最快反应时间。

推荐: