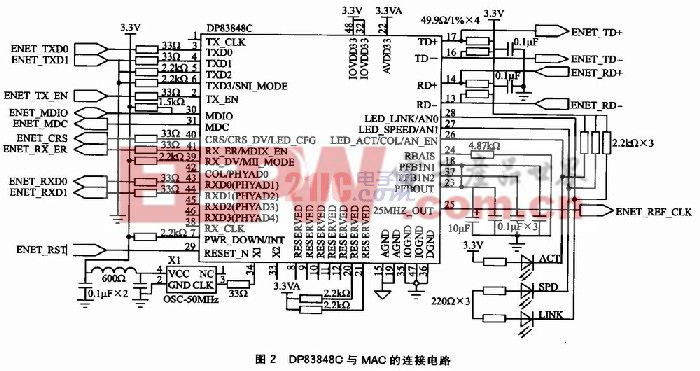

摘要:介绍了美国国家半导体公司的PHY芯片DP83848C的功能特性;给出了在RMII(Reduced Medium Independent Intece,精简的介质无关接口)模式下的硬件电及软件设计,以及在PCB布局布线过程中的注意事项。该设计为嵌入式系统中以太网底层的软硬件设计提供了参考,也为TCP/IP协议在嵌入式系统上的实现提供了硬件平台。

DP83848C是美国国家半导体公司生产的一款鲁棒性好、功能全、功耗低的10/100 Mbps单物理层(PHY)器件。它支持MII(介质无关接口)和RMII(精简的介质无关接口),使设计更简单灵活;同时,支持10BASE~T和100BASE-TX以太网外设,对其他标准以太网解决方案有良好的兼容性和通用性。

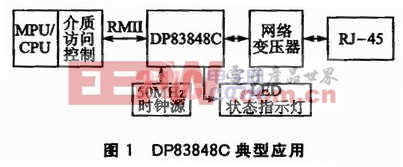

DP83848C的收发线各是一对差分线的以太网变压器后与网线相连。以太网变压器的主要作用是匹配、信号整形、网络隔离,以及滤除网络和设备双方面的噪音。典型应用如图1所示。

1.2 PCB布局布线 电阻和100 nF的去耦电容应靠近PHY器件放置,并通过最短的径到电源。如图3所示,两对差分信号(TD和RD)应平行走线,避免短截,且尽量长度匹配,这样可以避免共模噪声和EMI辐射。理想情况下,信号线上不应有交叉或者通孔,通孔会造成的非连续性,所以应将其数目降到最低;同时,差分线应尽可能走在一面,且不应将信号线所示。信号跨越一个分割的平面会造成无法预测的回电流,极可能导致信号质量恶化并产生EMI问题。注意,图3和图4中,阴影部分为错误方法。

推荐: