基于CAN总线的ECU电子控制单元的开发,也是现在最热门的研究。现在对CAN总线芯片的研究已经不再局限于单一芯片的研究,而是把所有的功能芯片都集中在一块芯片上实现一个完整的ECU的功能。

本项目目的是利用FPGA实现一款支持CAN2.0协议的总线控制器,完成一个通用的能够满足CAN2.0协议的CAN总线控制器软IP核,这样可以在以后的应用中方便的集成到其他系统中去。本文使用VerilogHDL语言,设计了一款支持CAN2.0协议的CAN总线控制器,并利用FPGA芯片在CAN总线网络中对其进行了测试,实现了设计目的。创新点为CAN_Registers设计中寄存器模块、位流处理器的收发部分功能、测试程序、基于该FPGA的CAN总线控制器的节点电等。

首先对CAN2.0协议进行了深入的分析,掌握了CAN总线协议的各部分内容;而后参照和分析了几种典型的CAN总线控制器的功能;最后选择PHILPS公司生产的CAN总线进行进一步的分析,掌握了它的各部分模块的功能。在这些基础上根据需要规划了所设计的CAN总线 设计描述和功能验证

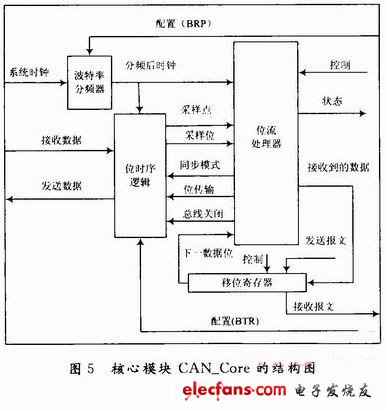

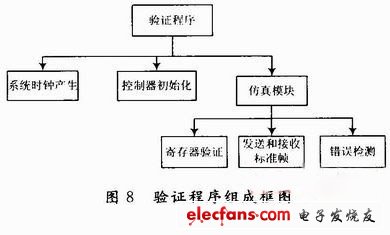

功能设计完成后,依据功能并参照CAN总线协议,将控制器划分为若干功能模块,明确了各个功能模块的作用。确定模块及其功能之后,用Verilog HDL语言实现了各模块的设计。接着,利用Modelsim对整个设计进行了功能验证。

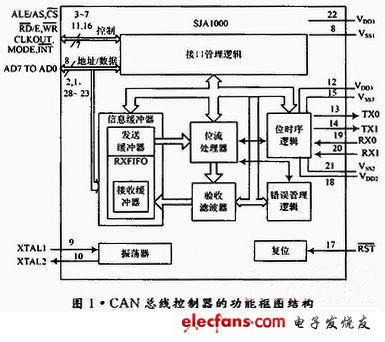

1.1.4 硬件验证配置到FPGA中以后,用所设计的基于FPGA的CAN总线控制器作为一个节点,与采用SJA1000作为控制器的节点电进行了通信测试,验证了所设计的CAN总线是PHILIPS公司于1997年推出的一种CAN总线控制器,用于汽车和一般中的控制器局域网络。SJA1000主要由以下几个部分构成:接口管理逻辑、发送缓冲器、接收缓冲器、接收滤波器、位数据流处理器、位时序逻辑、错误管理逻。SJA1000是双列直插式集成电,功能

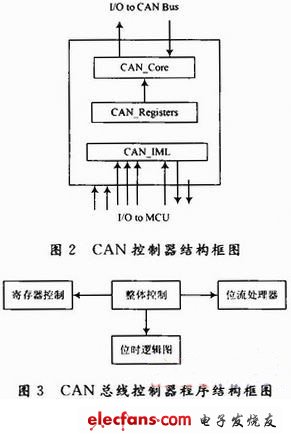

CAN_IML是CAN总线控制器接口逻辑,主要功能是解释来自微处理器的命令,控制CAN寄存器的寻址,向微处理器提供中断信息和状态信息。

图中Port_0_io_7到Port_0_io_0为地址/数据复合总线。Cs_can_i为片选输入信号。当Cs_can_i为0时允许访问CAN总线时,允许对寄存器进行赋值。Rd_i和Wr_i为微处理器的读使能信号和写使能信号。Irq_on为中断输出信号,用于中断微处理器。Rst_i为复位输入,用于复位CAN接口。Clkout_o为FPGA CAN控制器提供给微处理器的时钟输出信号,时钟分频寄存器可该引脚输出。Bus_off_on控制总线关闭和总线接口,Tx_o和Rx_i与收发器相连,向总线 CAN_Registers设计

设计的CAN总线控制器的寄存器模块包括以下寄存器:模式寄存器、命令寄存器、状态寄存器、中断寄存器、中断使能寄存器、总线、仲裁丢失捕获寄存器、错误代码捕获寄存器、错误报警寄存器、接收错误计数器、发送错误计数器、验收代码寄存器0~3、验收屏蔽寄存器0~3、接收信息计数器和接收/发送缓冲器。

接着使用ModelSim软件对所设计的各个模块和整个CAN总线控制器进行了功能仿真,仿真结果表明达到了设计目标。

仿真验证完成以后将其HDL CAN总线程序下载到FPGA中进行测试,目标芯片采用Cyclone系列的EP1C6Q240C8,为了验证所设计的FPGA CAN总线控制器,还设计了一款基于该FPGA的CAN总线控制器的节点电,然后利用所设计的节点电与其他3个利用SJA1000作为控制器的CAN总线节点进行了通信测试。所有的节点使用AT89S52

测试时,按动节点1上的开关并将该状态发送到节点2,在节点2上能显示对应的状态,反之也可。同时也可在节点2通过键盘输入某一代码,而在节点1上的数码管上显示相应的结果。该实验结果表明下载到FPGA中的控制器程序工作正常。

本项目利用Verilog HDL语言设计了一款CAN总线控制器芯片,并使用ModelSire软件对所设计的CAN总线控制器进行了功能仿真;之后为了验证设计,还编制一个验证程序,并将验证之后的设计配置到了FPGA中;最后用所设计的基于FPGA的CAN总线控制器制作了CAN节点,并与其他采用SJA1000为控制器的CAN节点进行了通讯测试,实现了CAN总线良好的工作,验证了设计的正确性。

推荐: